アンプを作ろうか?

その3-5 差動増幅回路の完成

前回の回路は出力波形が歪んでしまう原因は、トランジスタ Q2 の逆流。 そして見えにくい要因としてトランジスタが飽和していると言うことでした。 解決策は、Q2 の動作点をもっと Vcc 側(+6[V]側)にシフトすることです。 そこで、次段にエミッタ接地回路を接続して動作範囲をマイナス側まで拡張します。

(1) エミッタ接地回路

図2 エミッタ接地回路を追加した回路

図1 がエミッタ接地回路を追加した差動増幅回路です。 カレントミラー回路の格好がちょっと違いますよね?今までは Q3 のベースとコレクタが接続されていましたが 今回は Q4 のベースとコレクタが接続されています。 これは、エミッタ接地回路の出力が反転されるため、前段の差動増幅段の出力を反転する必要があるためです (- × - = + ですね!)。 よって、出力信号の取り出しを Q2 から Q1 に変更することによって反転、つまりゲインをマイナス倍します。

さてさて、エミッタ接地回路の Q7 の Vbe はほぼ 0.65[V] ですから、 Q7 のベース電位はほぼ「Vcc - 0.65[V]」になります。 Q1 のコレクタ電位は Q7 のベース電位なので「Vcc - 0.65[V]」まで引き上げられることになります。 Q1 のエミッタは入力 Vi1 が 0[V] だとすると -0.65[V] なので 6[V] が Q1 の Vceとなります。 これで十分に線形領域で動作できる Vce を得ることがでそうです。 まあ、その代わりカレントミラーを構成している Q3 の Vce が低下しますが、 動かない回路作ってもしょうがないのでここはトレードオフです。

では、エミッタ接地回路を接続した場合の差動増幅段のゲインはどうなったのでしょうか? 差動増幅回路の Q3 の負荷は、Q1 の出力インピーダンス ro1、Q3 の出力インピーダンス ro3 に加え、 次段に接続したエミッタ接地回路の Q7 の入力インピーダンス ri となります。 よって、差動増幅段のゲイン Av1 は、

となりますね。 このように多段で回路を接続していくと前後の回路が影響を受けますので少しややこしくなっていきます。

(2) 入力インピーダンスの計算

さて、肝心の ri はどのくらいなんでしょうか? エミッタ接地の入力インピーダンスは以下のように計算できます。 ここでまたもや例の式の登場ですw(それほど大事な式なのですね)

Ic = hfe * Ib ですから、

Ib = Is / hfe * exp(Vbe / Vt)

Ib に関する式に変形できました。これを Vbe で微分します。

ここで、「gm = Ic / Vt」なので、

さて、入力インピーダンスとはトランジスタのベースから見たインピーダンスですので、 ベースに流れる電流と電圧から計算することができます。つまり、

というわけで先ほど計算した、dIb / dVbe の逆数となります。

よって、トランジスタの入力インピーダンス ri は

となります。

さてさて、gm の計算にはエミッタ接地回路に流れる電流値 Ic が必要になります。回路に負帰還がかかっているとすると、 信号を入れないとき(vi1 = 0)の出力電圧 Vo は 0[V] になるはずですので R5(2.2[kΩ])の両端にかかる電圧は 6[V] です。よって Ic は、

よって、Q7 の gm は、

となります。hfe = 100 として入力インピーダンス ri を計算すると

となります。最終的な差動増幅回路のゲイン Av1 は

ここで、ri ≪ ro1 // ro3 なので、

しっかし、ゲインが大きく下がっちゃいましたね・・・w

でも、エミッタ接地回路の増幅率がありますのでご心配なくです。

また、カレントミラーの恩恵であるエミッタ接地回路の電流駆動でトランジスタを強力に線形で増幅させます。

なんせ、「Ic = hfe * Ib」の Ib をカレントミラーから直接供給して駆動しますので歪み率低減の効果を期待できますね。

(3) エミッタ接地回路のゲイン

エミッタ接地回路のゲイン Av2 は前々回位で説明したとおりで以下のようになります。

Q7 の gm は先ほど入力インピーダンス ri を計算したときに「gm = 105[mS]」と求めました。 というわけで、ゲイン Av2 は

です。回路全体の増幅率 Av は、差動増幅回路のゲイン Av1 とエミッタ接地回路のゲイン Av2 をあわせたものなので、

Av2 = -231[倍] ≒ 47[dB]

Av = -37[倍] * -231[倍] = 8547[倍]

Av = 31[dB] + 47[dB] = 78[dB]

というわけで、「ゲイン 8547[倍](78[dB])」の差動増幅器が出来上がりました。

図2 差動増幅器のゲインと、全体のゲイン

図6 ゲイン 2倍 で動作させてみる!

図6 はシミュレーション結果ですが、今回はしっかりと増幅されています! うーん・・・ゲインも高いしオペアンプらしくなってきましたが、実際に使用するためにはもう少し工夫が必要になります。

(4) 電流バッファを追加するよ!

エミッタ接地回路の出力インピーダンスは R // ro5 になるので、出力インピーダンスが高すぎます。 今回は、約 2.2[kΩ] ですね(R ≪ ro5 としました)。

一般的なヘッドホンの抵抗値は 50[Ω] 程度ですので、これでは大きすぎます。 そこで、トランジスタであればエミッタフォロアの登場ですが、私の趣味と熱暴走の危険の少ないという理由で FET にしますw

ソースフォロア回路についてはだいぶ前に説明してますのでそちらを参考ください。 違う点としては±6[V]の両電源ですのでプッシュプル構成となります。 かの有名なAB級プッシュプルってやつですので動作の説明はいらないかなと思います。 (知らない人はどこかのページで見てくれw)

具体的な組み込み方ですが、図4 のようにエミッタ接地回路の途中にダイオード2個を挿入してそれをバイアスとします。 あとは、発振するかもしれないのでおまじないの 10[Ω] を介して、N型、P型のFET でプッシュプル 回路を作ります。簡単でしょ?

図4 電流バッファを組み込んだ回路

さあ、これで完成!といきたいんですが、このままじゃ発振してしまいますw

(5) 発振と位相補償

図5 ステップ応答

(ゲイン : 6[dB]、負荷 : なし)

図5 はステップ応答(方形波を入力した場合の出力)のシミュレーションですが見事に発振していますw

では、負帰還をかけない状態での各周波数特性「オープンループゲイン、位相」を見ていきましょう。 ちなみに負帰還をかけているときは「クローズドループゲイン」といいます。 負帰還の帰還回路の帰還率、帰還率とオープンループゲインの積「ループゲイン」とまあいろいろあるわけですが、 ひとまずオープンループゲインについてみていきましょう。

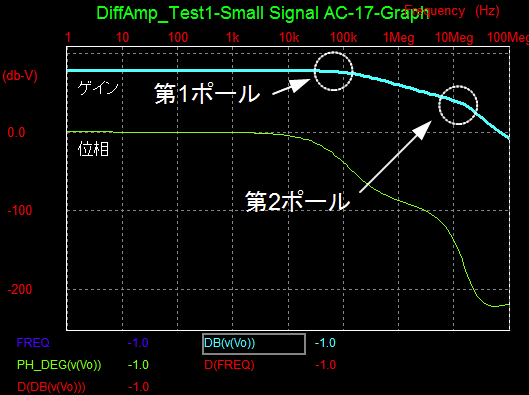

図6 オープンループゲイン、位相

図6-1 ポール

図6 のようにゲイン、位相を各周波数ごとにプロットしたものを「ボード線図」と言います。 また、ゲインが折れ曲がるところを「極(ポール)」と言います。 因みにポールは2つありますね? これらを順番に第1ポール、第2ポールといいます。

負帰還とは入力の逆相(-180°位相が遅れた)の信号を入力に戻すと言うことです。 回路中で位相が -180°以上遅れた場合、負帰還の -180°と合わせて -360°の遅れとなり正帰還となってしまいます。 このとき、入力した信号よりも大きな信号が戻ってきた場合(ゲインが 1 以上)、 入力信号が際限なく大きくなってしまい発振してしまうわけです。 よって、発振する条件は「位相が -180°遅れた時のゲインが 0[dB] 以上」あるときです。

因みに、ゲイン 0[dB] の時の位相が -180[dB] からどのくらい余裕があるかを「位相余裕」と言い、 位相が -180[dB] の時のゲインが 0[dB] からどのくらい余裕があるかを「ゲイン余裕」と言います。 当然ですが余裕が 0 以下の場合発振します。

これをふまえて、もう一度図を見てみましょう。 図6のゲイン余裕は -30[dB]、位相余裕は -40°と見事に発振する条件がそろっていますね?

図7 位相補償

さて、このままではまずいので「位相補償」を行ってもっと余裕を稼ぎましょう! 位相補償には何種類かあるのですが、基本的に周波数特性を低下させる手法をとります(狭帯域化といいます)。

さて、図7 の C2 のようにコンデンサを挿入します。 なぜかと言いますと、ミラー効果によってコンデンサの見かけの容量が増えるからなのですが・・・ これについては、ミラー効果について説明した方がいいですね。

(6) ミラー効果

図8 ミラー効果

ミラー効果とは、図8のような増幅度「-A[倍]」の増幅器にコンデンサ C を接続した場合、 その容量が入力から見た場合、見かけ (A + 1) 倍されて見えるという現象です。 (うんちくとしてミラーさんが発見したんでミラー効果です。カレントミラーのミラーとは違いますよw)

さて、どうしてそうなるのかを見てみましょう!(増幅器の入力インピーダンスは∞として考えます)。 出力電圧 Vo は、

コンデンサにかかる電圧 Vc は、入力電流 Ii がコンデンサのインピーダンス Zc に流れますので、

従って、入力電圧 Vi は Vo + Vz になりますので、

従って、入力電圧 Vi は Vo + Vc になりますので、

Vi = Vo + Vc = -A * Vi + Vc

これを Vi について整理します。

Vi + A * Vi = Vc

Vi * (1 + A) = Vc

Vi = Vc / (1 + A)

入力インピーダンス ri は、Vi / Ii ですので、Vz をもどして、

入力インピーダンス ri は、Vi / Ii ですので、Vc をもどして、

ri = Vi / Ii = Zc / (1 + A)

です。コンデンサのインピーダンス Zc は 1 / jωC ですので、

となります。 何を意味しているかと言いますと、負のゲインをもつ増幅器の入出力間に接続されたコンデンサ C は、 入力から見るとみかけ (1 + A)[倍] される。ということです。

本当に増えるわけじゃありません。増幅回路によって、「そう見える」だけです。勘違いなさらぬように・・・ (慣性系の運動のようなものです。コリオリの力とかと一緒?w)

観測側から見るるとあたかもそう見えるだけに過ぎませんので、増幅回路が正常に動作しなければ成立しません。 しかし、今までの計算は増幅回路として動作しているのを前提としていますし、そもそもこの回路は増幅回路なので自ずと成立してしまいますよね?

何となく挿入した位置の意味がわかってきましたか? そうですね、エミッタ接地回路は負のゲインを持つ増幅器です(ゲインは - gm * R でしたよね?)。 よって、入出力間に接続されたコンデンサはエミッタ接地回路のゲイン倍されて見えると言うことです。

たとえば 220[pF] のコンデンサを挿入するとエミッタ接地回路のゲインは -231[倍] でしたので、 入力から見た見かけのコンデンサの容量 C' は

となります。

図9 オープンループゲイン、位相

(ミラー効果を利用した位相補償)

図10 オープンループゲイン、位相

(51nF を 図11 のように挿入した場合)

図11 図10のシミュレーションに使用した回路

図9は、図7のオープンループゲイン、位相。図10はミラー効果の確認のために 51[nF] を図11のように挿入した場合の オープンループゲイン、位相をシミュレーションしたものです。 比べてみますと確かに第1ポールはほぼ一致しています。 ただ、第2ポールの位置が異なり、ミラー効果を利用したほうが位相余裕が大きくなっています。 これは、第1ポールが低域に移動して、さらに第2ポールが高域へ移動する「極分離」という効果によるためです。 このように単純に前段に LPF を挿入するよりミラー効果を利用した方が極分離があるため負帰還の安定度はよくなります。

さてさて、位相補償の効果はありましたが「位相余裕 12°」とは依然厳しいです。 一般的に位相余裕は 40°以上はほしいところです。

(7) さらなる位相補償

図12 ヘッドフォンの等価回路を接続した回路

それでは、ヘッドホンの等価回路を負荷にしてみます。 (この等価回路はネットで拾ってきました・・・w 作ってくれた人には感謝!!)

図13 ステップ応答

(ゲイン : 6[dB]、負荷 : ヘッドフォンの等価回路)

図13 は、ゲイン 6[dB]に設定したときのステップ応答ですが、うーん気に食いません! ちょっと角がありますよね?このように角が立つことを「リンキング」といいます。 リンキングは発振するの手前なのであんまりよろしくありません。

図14 オープンループゲイン、位相

(負荷 : ヘッドフォンの等価回路)

図14 はオープンループゲインですが、うーん、位相余裕 8°とは・・・さらに少なくなっていますねぇ。

というわけで、シャント抵抗とコンデンサによるフィルタ回路を挿入します(みんなゾーベルフィルタと呼んでいます)。

図15 ゾーベルフィルタによる補償(R10、C3)

図15 の R10 がシャント抵抗となります。 C3 はR10 によけいな DC 成分が流れるのを抑制します。まあ、だまされたと思って入れてみましょう。

図16 オープンループゲイン、位相

(ゾーベルフィルタを追加後)

どうでしょうか?図16 のシミュレーション結果では見事に位相余裕が 60°にまで改善されました。 効果としては高周波域の負荷変動を抑える効果があると思っていただければと思います。 (これをゾーベルフィルタと呼ぶには私的に違和感があるのですが・・・w)

これで完成か? いやいや、ここはとことんいじめてみましょう!w

図17 意地悪テストで 0.1[uF]を負荷にしてみた

図18 0.1[uF]ステップ応答 見事に発振w

(ゲイン : 6[dB]、負荷 : 0.1[uF])

図17 は 0.1[uF] のコンデンサを負荷とした場合ですが、図18 のように発振していますw このように、負帰還はコンデンサを代表する遅れ要素にとことん弱いのです。 そこで、このような意地悪テストを実際によく行います。 0.1[uF] は相当に重い容量性負荷なので、「これで発振しなかったら、まず発振しない回路だ!」と言うことができます。

もうちょっとい、がんばりますか・・・というわけで、帰還抵抗 R11 へ並列にコンデンサ C4 を追加します。 一見 LPF ですが位相補償という観点からは、帰還回路で位相が進みますので「微分型位相補償」と呼ばれます。 0.1[uF] の負荷で位相が遅れた分、位相を進めてカバーしたと思ってください。

図19 微分型位相補償(C4)

図20 位相補償後の周波数特性図

(ゲイン 6[dB]、負荷 : 0.1[uF])

さてさて、図19、20 のような結果となりました。 どうでしょうか? 0.1[uF] の負荷でも発振することなく安定しています。

図21 周波数特性

(ゲイン : 6[dB]、負荷 : なし)

図21 はゲイン 6[dB](2[倍])の周波数応答です。位相補償の結果、 帯域は狭まりましたがオーディオに必要な可聴域 20 ~ 20[kHz] は余裕でカバーできています。

狭帯域化、ゾーベルフィルタ、微分型位相補償などいっぱい位相補償しましたw。 位相補償は今回の中でも屈指の難しさです(数学的な知識もいりますし、古典制御など周辺知識含めまじめに書くと本一冊では収まりません・・・)。 私も不勉強で完全に理解しているとは言えないのがお恥ずかしいところですが、 大概の場合は今回の方法で発振を回避できるかと思います。 とりあえず今回の説明で「何を目的に位相補償しているのか?」程度は理解していただけると思いますが、 私も勉強のため位相補償に関しては別途小ネタで詳細をやっていきたいと思っています。 また興味がある方は是非とも他のホームページ、専門書で補完していただきたいです(ちょっと自信がないんでw)。

次回は、実際にこの回路を製作しましたので、最終的な回路図の紹介と特性の評価を行います。