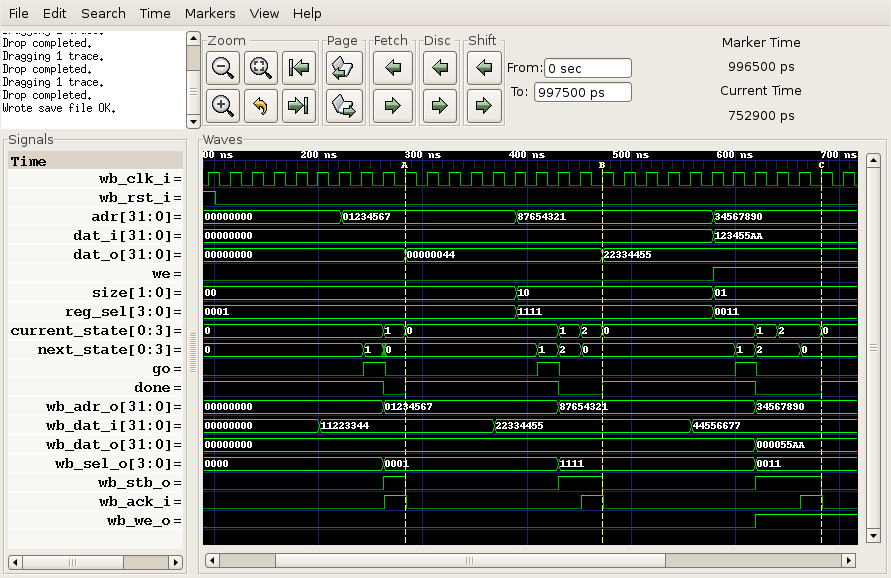

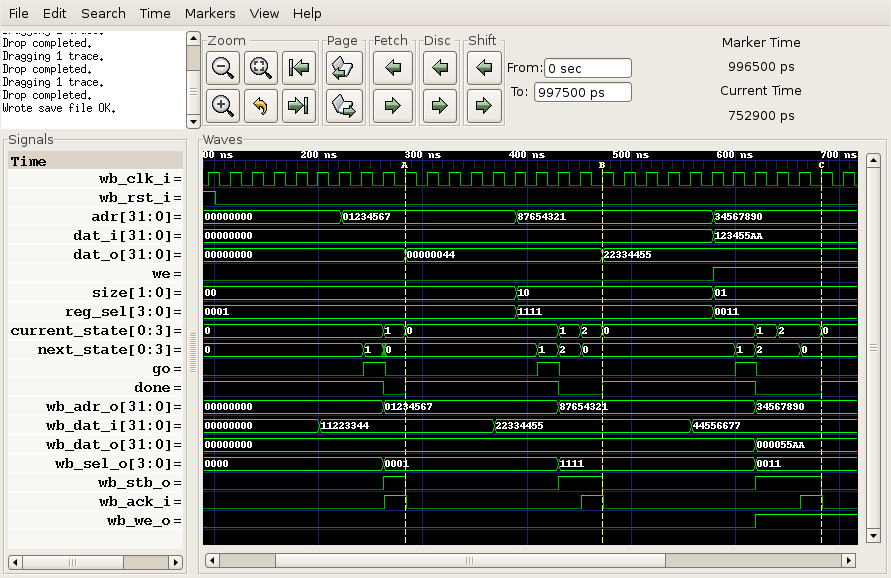

-- WISHBONE MASTER interface: WB_CLK_I : in システム同期クロック WB_RST_I : in 同期RESET WB_ADR_O : out WISHBONE アドレス値 WB_DAT_I : in WISHBONE 読み込み入力 WB_DAT_O : out WISHBONE 書き込み出力 WB_WE_O : out WISHBONE 処理指定 0/1 = Read/Write = 読み込み/書き込み WB_SEL_O : out WISHBONE 処理時のByte位置指定 WB_STB_O : out WISHBONE 処理開始 WB_ACK_I : in WISHBONE 処理終了 -- Other port interface: ADR : in 処理アドレスの設定値 DAT_I : in 書き込み時の設定値 DAT_O : out 読み込み時の結果値 WE : in 処理指定 0/1 = Read/Write = 読み込み/書き込み SIZE : in 処理Byte長 00/01/10/11 = 1Byte/2Byte/4Byte/設定禁止 GO : in 処理開始 (クロックに同期した1パルスを入力すると処理が開始される) DONE : out 処理終了なら'1'