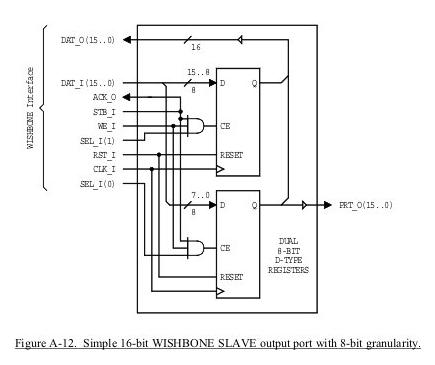

※図は仕様書(wbspec_b3.pdf)の図A-12を引用

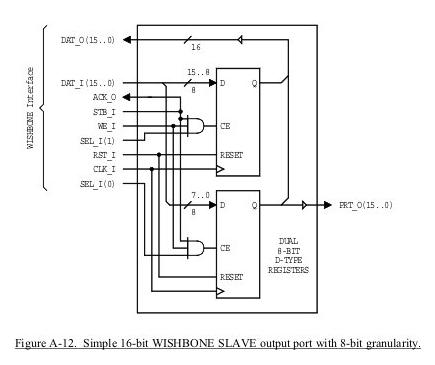

※図は仕様書(wbspec_b3.pdf)の図A-12を引用

file:WBOPRT16.vhd

仕様書のサンプルを自分流の記述スタイルに修正してあります。

--*************************************** --* Title : WBOPRT16.vhd * --* Designer : Osamu Kawashima * --* Created Date : 2007.02.26 * --* Modified Date: ----.--.-- * --* * --* Copyright Osamu Kawashima * --*************************************** library ieee; use ieee.std_logic_1164.all; entity WBOPRT16 is port ( -- WISHBONE SLAVE interface: WB_CLK_I : in std_logic; WB_RST_I : in std_logic; WB_DAT_I : in std_logic_vector(15 downto 0); WB_WE_I : in std_logic; WB_SEL_I : in std_logic_vector(1 downto 0); WB_STB_I : in std_logic; WB_ACK_O : out std_logic; WB_DAT_O : out std_logic_vector(15 downto 0); -- Output port (non-WISHBONE signals): PRT_O : out std_logic_vector(15 downto 0) ); end WBOPRT16; architecture RTL of WBOPRT16 is constant ZERO32 : std_logic_vector(31 downto 0) := (others=>'0'); signal dat_h : std_logic_vector(7 downto 0); signal dat_l : std_logic_vector(7 downto 0); begin process(WB_CLK_I) begin if WB_CLK_I'event and WB_CLK_I='1' then if WB_RST_I='1' then dat_h <= (others=>'0'); elsif (WB_STB_I and WB_WE_I and WB_SEL_I(1))='1' then dat_h <= WB_DAT_I(15 downto 8); else dat_h <= dat_h; end if; end if; if WB_CLK_I'event and WB_CLK_I='1' then if WB_RST_I='1' then dat_l <= (others=>'0'); elsif (WB_STB_I and WB_WE_I and WB_SEL_I(0))='1' then dat_l <= WB_DAT_I(7 downto 0); else dat_l <= dat_l; end if; end if; end process; WB_ACK_O <= WB_STB_I; WB_DAT_O(15 downto 8) <= dat_h; WB_DAT_O( 7 downto 0) <= dat_l; PRT_O(15 downto 8) <= dat_h; PRT_O( 7 downto 0) <= dat_l; end RTL;