| Name | bit's | Comment |

| REG_CTRL_INIT | 8 | コントロールレジスタの初期値設定 Bit7 Reserved '0' Bit6 Reserved '0' Bit5 Reserved '0' Bit4 Reserved '0' Bit3 Reserved '0' Bit2 Reserved '0' Bit1 IRQ_ENABLE (0/1=Disable/Enable) Bit0 Enable (0/1=Disable/Enable) |

| Name | I/O | bit's | Comment |

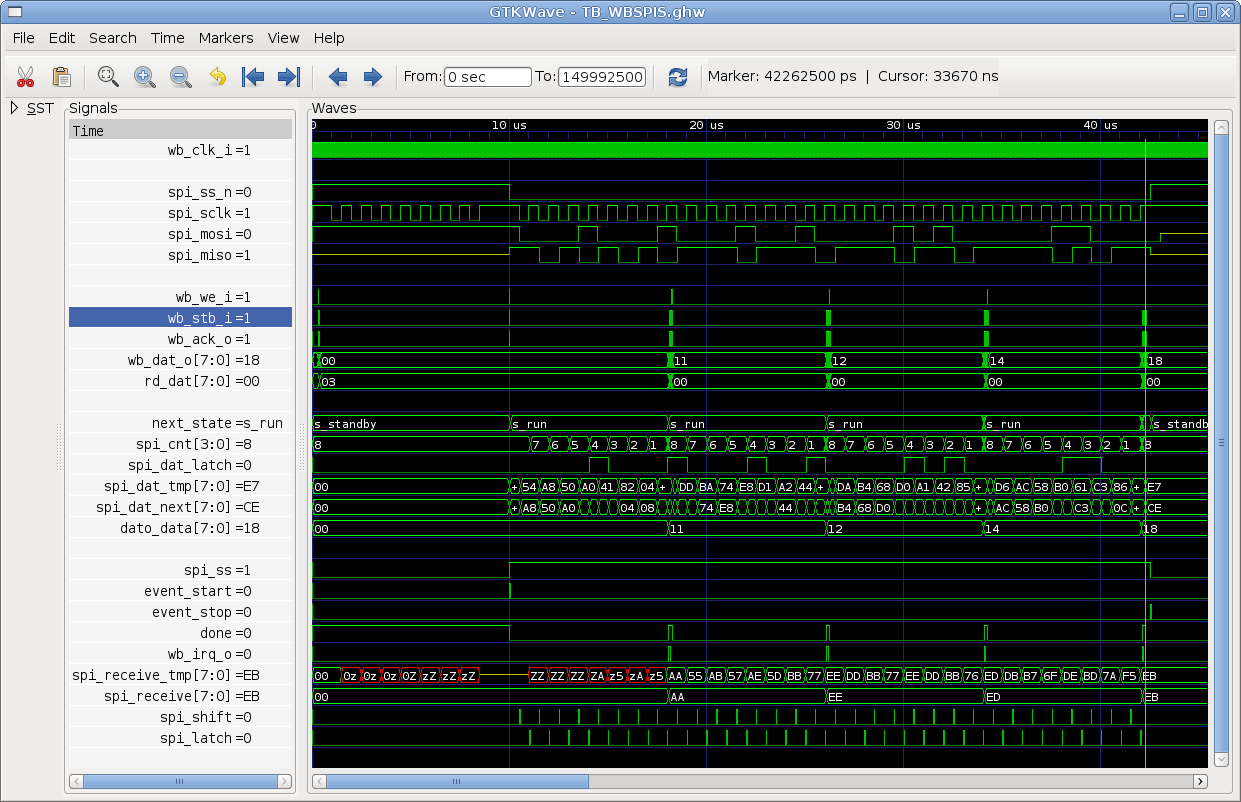

| WB_CLK_I | in | 1 | SYSCLK (シミュレーション時は48MHz) |

| WB_RST_I | in | 1 | RESET |

| WB_ADR_I | in | 8 | アドレス 00 データレジスタ 書き込み値は 01 制御レジスタ 読み書き可能。Bit情報はREG_CTRL_INITを参照。 02 状態レジスタ 読み出しのみ。Bit7:1は'0'。Bit0はWB_IRQ_Oの値。 |

| WB_DAT_I | in | 8 | データIn |

| WB_WE_I | in | 1 | 0/1=Read/Write |

| WB_STB_I | in | 1 | Strobe 0/1=無効/WishBone-I/F有効 |

| WB_ACK_O | out | 1 | Ack |

| WB_DAT_O | out | 8 | データOut |

| WB_IRQ_O | out | 1 | 割り込み発生時に'1'。 制御レジスタのIRQ_ENABLE='1'の時に使える |

| Name | I/O | bit's | Comment |

| SPI_SS_N | in | 1 | Active Low(負論理) |

| SPI_SCLK | in | 1 | Serial Clock |

| SPI_MOSI | in | 1 | Master-Out Slave-In |

| SPI_MISO | out | 1 | Master-In Slave-Out |

| Name | I/O | bit's | Comment |

| SPI_SS | out | 1 | SPI_SS_Nを同期処理した信号(正論理) |

| EVENT_START | out | 1 | SPI_SSの立ち上がり時に1パルス出力 |

| EVENT_STOP | out | 1 | SPI_SSの立ち下がり時に1パルス出力 |

| DONE | out | 1 | SPI通信で1Byte送受信すると'1'。 送信値を書くと'0' |