WBSPIM.vhd

概要

WISHBONE-I/FのSPI-Master通信モジュール。

FPGA外部のSPIなデバイスとの通信用に使う。

※川島が趣味で設計したモジュール。自己責任で使用する事を許可します。(^^;

注意

- 送信データの書き込みタイミング(WB_STB_I)は1CLK分を想定(2CLK以上の運用禁止)。

レジスタの説明

レジスタは8bit長です。

C_DATA : 00H : 送信/受信値 (W/R)

bit7-0 : 書けば送信値として送信。その後読めば受信値が読み出せます。

C_CTRL : 01H : 割り込み制御とSPI_SS_N の制御 (W/R)

bit0 : WB_IRQ_O出力制御 (0/1=禁止/許可)

IRQ状態を出力するかを設定できる

bit1 : SPI_CS出力 (0/1=禁止/許可→SPI_SS_NS=H/L)

bit7-2 : '0'固定

※RESET初期値はREG_CTRL_INITで設定可能

C_DIV : 02H : ボーレート設定値 (W/R)

bit3-0 : ボーレート値 (CLK=WB_CLK_I)

0 →CLK/2

1 →CLK/4

2 →CLK/8

3 →CLK/16

4 →CLK/32

5 →CLK/64

6 →CLK/128

7 →CLK/256

8 →CLK/512

F-9→CLK/512

bit7-4 : '0'固定

※RESET初期値はREG_DIV_INITで設定可能

C_STAT : 03H : 状態値が読めます。 (-/R)

bit0 : IRQ状態 (0/1=送信終了IRQ無し/有り)

bit7-1 : '0'固定

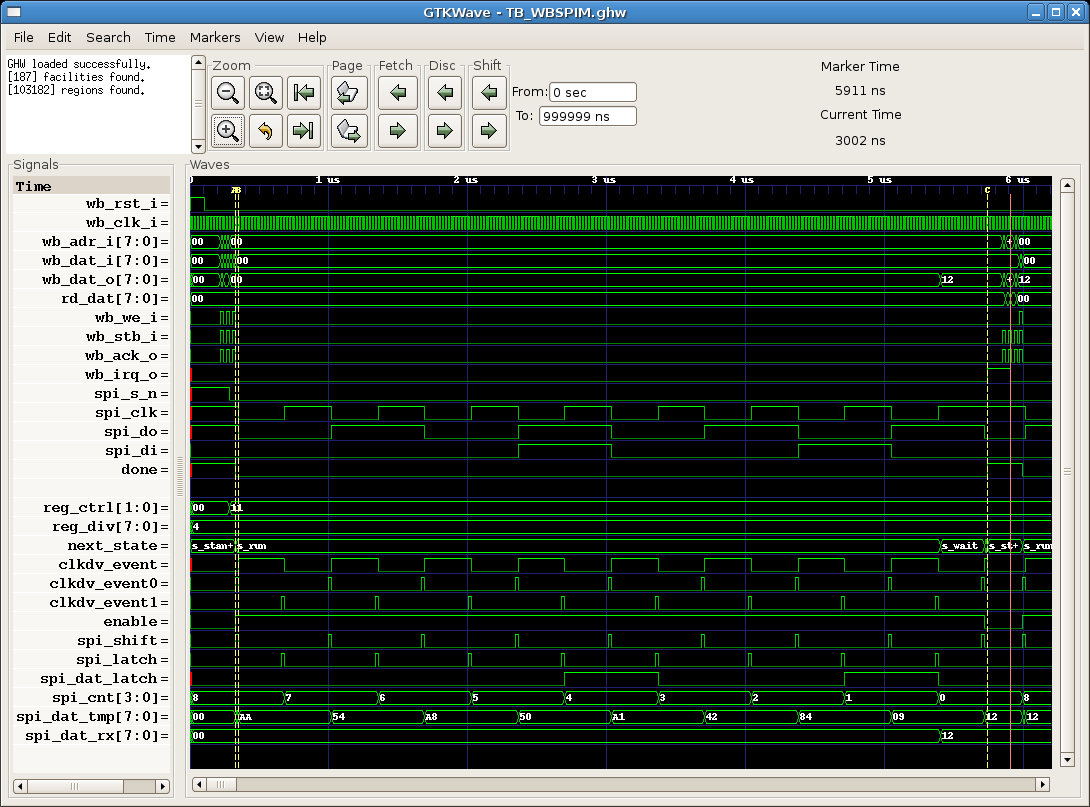

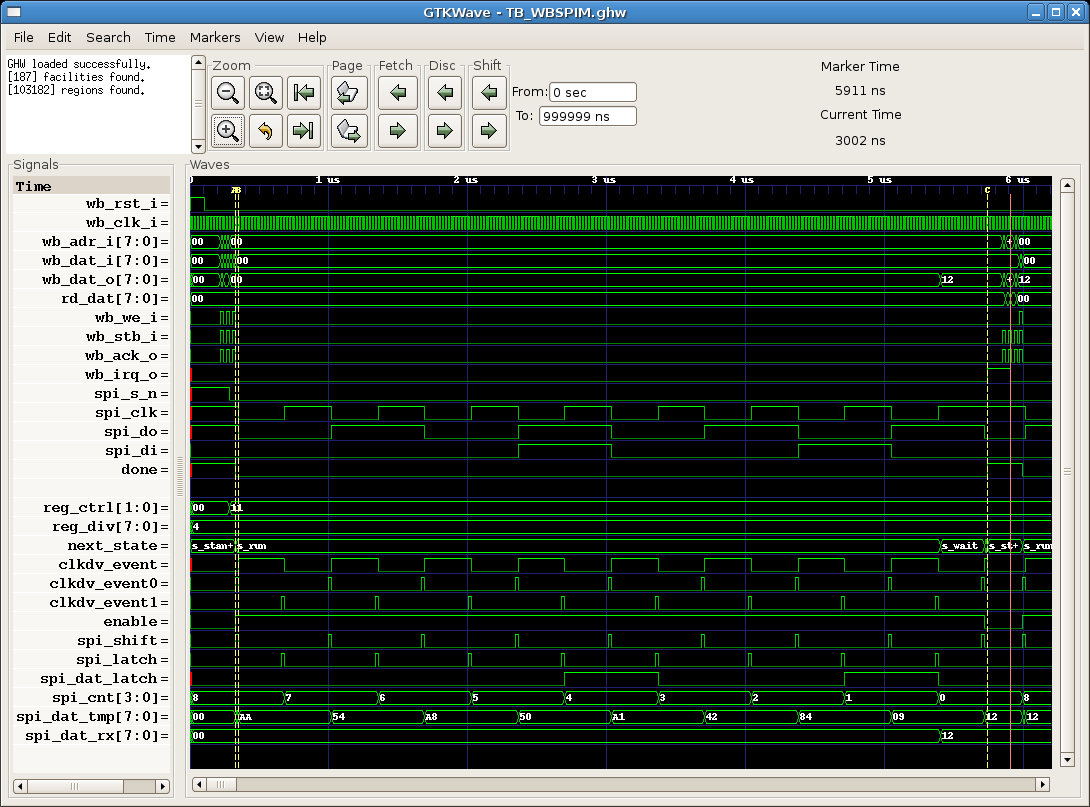

シミュレーション波形

File's

参考

履歴

- 1.7-2021/02/01

Makefile修正

- 1.6-2011/08/16

「レジスタの説明」を追加

- 1.5-2011/08/14

「WBSPIMM.vhd」へのリンクを追加

- 1.4-2011/07/29

「注意」を追加

- 1.3-2008/05/16

連続低速でSPI通信をした時にBYTE間のspi_clk幅が狭いので対策をする

- 1.2-2008/04/14

spi_shift信号が1回余分なので対処,出始めのタイムラグ改善

- 1.1-2008/04/12

出始めのタイムラグ改善とgeneric文とDONE信号によりステートマシーンからの制御制を良くさせた

- 1.0-2008/04/08

初版

現バージョンは出始めのタイムラグがいまいち